High-High-Speed: PCIe-Gen-6-Spezifikation festgezurrt

PCIe 6.0 wird zunächst im High-End eingesetzt werden. (Quelle: PCI-SIG)

PCIe 6.0 wird zunächst im High-End eingesetzt werden. (Quelle: PCI-SIG)Das Industrie-Konsortium PCI-SIG (Peripheral Component Interconnect Special Interest Group) hat die offiziellen Spezifikationen für PCIe 6.0 veröffentlicht. Die sechste Version der internen Express-Verbindung gilt als die bedeutendste Überarbeitung des PCI-Express-Standards seit 3.0 im Jahr 2010. Erste Lösungen werden 2024 erwartet.

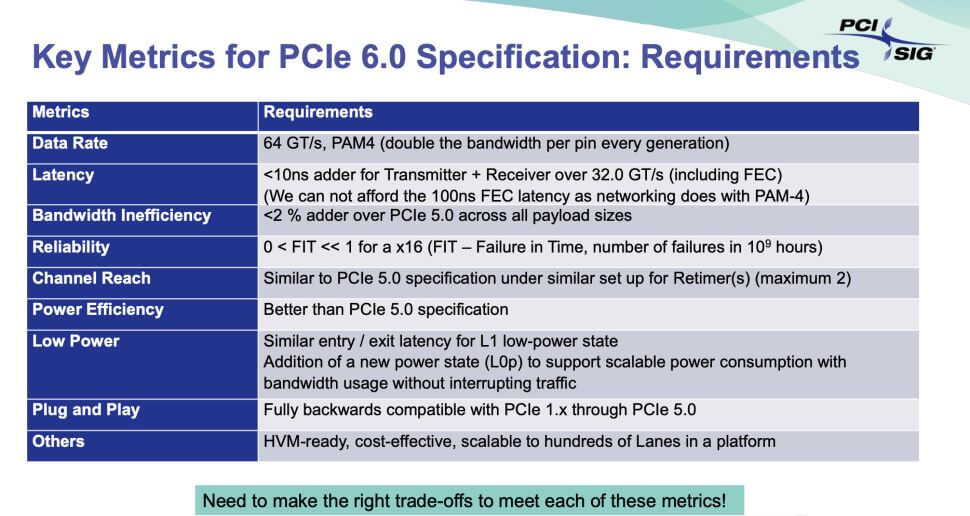

PCIe 6.0 erreicht Datenübertragungsraten von 64 Gigatransfers pro Sekunde (GT/s) pro Spur (Lane). Dies ergibt eine Gesamtbandbreite von 256 GByte/s über 16 Lanes in beide Richtungen. Um solch hohe Geschwindigkeiten zu erreichen sowie die Zuverlässigkeit und Effizienz der Vorgänger aufrechtzuerhalten, verwendet PCIe 6.0 erstmals die Pulsamplituden-Modulation mit vier Stufen (PAM-4), die bisher hauptsächlich für High-End-Netzwerktechnologien verwendet wurde, für die Forward-Error-Correction (FEC). Ebenso integriert PCIe 6.0 Technologien wie Flit (Flow Control Unit)-Kodierung auf Basis von PAM-4, Cyclic Redundancy Check (CRC) oder L0p-Verzögerungsmodule zur Stabilisierung der Leistung.

Die Spezifikationen für PCIe 6.0 tabellarisch. (Quelle: PCI-SIG)Die Aufrechterhaltung der Signalintegrität bei 64 GT/s mit PAM-4 wird als ziemlich schwierig beschrieben, da diese Codierungsmethode fehleranfälliger ist als die traditionell von PCIe verwendete NRZ-Codierung (binary non-return-to-zero). Da PCIe eine Schnittstelle für interne Konnektivität ist, muss sie nicht nur schnell, sondern auch mit geringer Latenz sein. Zu diesem Zweck muss die FEC-Methode von PCIe 6.0, die durch CRC weiter verbessert wurde, eine niedrige Latenz gewährleisten und gleichzeitig robust genug sein, um die unvermeidlichen Bitfehler zu beheben, die bei solch hohen Geschwindigkeiten bei der Verwendung von PAM-4 auftreten. Gleichzeitig soll Abwärtskompatibilität zu Vorgängergenerationen gewährleistet werden.

Die Spezifikationen für PCIe 6.0 tabellarisch. (Quelle: PCI-SIG)Die Aufrechterhaltung der Signalintegrität bei 64 GT/s mit PAM-4 wird als ziemlich schwierig beschrieben, da diese Codierungsmethode fehleranfälliger ist als die traditionell von PCIe verwendete NRZ-Codierung (binary non-return-to-zero). Da PCIe eine Schnittstelle für interne Konnektivität ist, muss sie nicht nur schnell, sondern auch mit geringer Latenz sein. Zu diesem Zweck muss die FEC-Methode von PCIe 6.0, die durch CRC weiter verbessert wurde, eine niedrige Latenz gewährleisten und gleichzeitig robust genug sein, um die unvermeidlichen Bitfehler zu beheben, die bei solch hohen Geschwindigkeiten bei der Verwendung von PAM-4 auftreten. Gleichzeitig soll Abwärtskompatibilität zu Vorgängergenerationen gewährleistet werden.

Leistungshungrig, und dennoch effizient

Kurz: Die Einführung von PAM-4 (und allem, was dazu erforderlich ist) wird unweigerlich die Kosten der PCIe 6.0-Implementierung erhöhen und PCIe-6.0-Controller und andere physische Schichten leistungshungriger machen als PCIe 5.0. Allerdings verspricht die neue Technologie eine höhere Gesamtenergie-Effizienz als die von PCIe 5.0 zu erzielen, sodass es für viele Anwendungen sinnvoll sein wird, auf PCIe 6.0 umzusteigen, insbesondere in Fällen, in denen die Anzahl der Lanes reduziert werden kann.

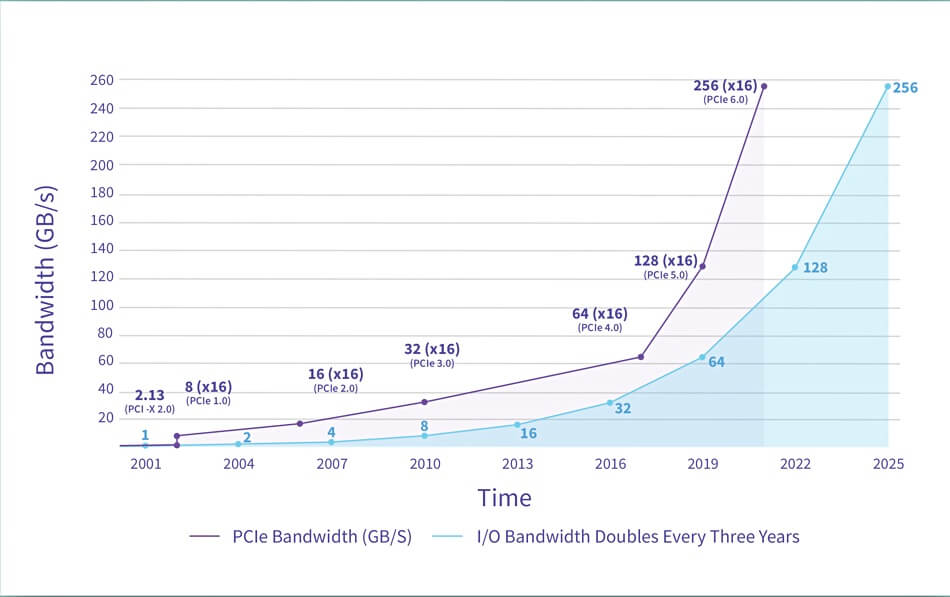

Die Entwicklung der PCIe-Technologie historisch. (Quelle: PCI-SIG)Angesichts aller Komplexitäten und vieler technischer Änderungen von PCIe Gen6, dürfte es im professionellen Bereich zunächst für kosten-unempfindliche Anwendungen im High-Performance-Computing (HPC) und für künstliche Intelligenz (KI) eingesetzt werden.

Die Entwicklung der PCIe-Technologie historisch. (Quelle: PCI-SIG)Angesichts aller Komplexitäten und vieler technischer Änderungen von PCIe Gen6, dürfte es im professionellen Bereich zunächst für kosten-unempfindliche Anwendungen im High-Performance-Computing (HPC) und für künstliche Intelligenz (KI) eingesetzt werden.

Start im High-End-Computing

Im Allgemeinen wird PCIe 6.0 aufgrund der Komplexität der Implementierung zunächst wohl nur für kosten-unempfindliche Anwendungsbereiche verwendet werden, darunter künstliche Intelligenz (KI), maschinelles Lernen (ML) oder Internet-of-Things (IoT), im High-Performance-Computing (HPC) für High-End-SSDs, in Industrien wie der Automobil-Entwicklung, Luft- und Raumfahrt oder im Militär-Wesen.

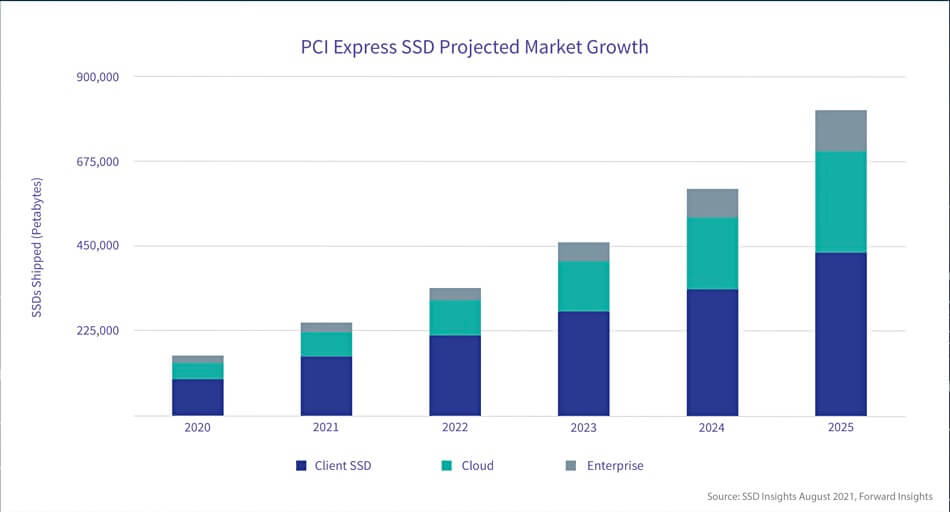

Die Marktprognosen für PCIe. (Quelle: PCI-SIG)»Da der PCI-Express-SSD-Markt bis 2025 voraussichtlich um 40 Prozent auf über 800 EByte wachsen wird, erfüllt PCI-SIG weiterhin die zukünftigen Anforderungen von Speicheranwendungen«, sagt Greg Wong, Gründer und Principal Analyst bei Forward Insights. »Mit dem Übergang der Speicherbranche zu PCIe 4.0 und kurz vor der Einführung der PCIe-5.0-Technologie, werden Unternehmen damit beginnen, PCIe 6.0 in ihre Roadmaps aufzunehmen, um ihre Produkte zukunftssicher zu machen und die Vorteile der hohen Bandbreite und niedrigen Latenz der PCI Express-Technologie zu nutzen.«

Die Marktprognosen für PCIe. (Quelle: PCI-SIG)»Da der PCI-Express-SSD-Markt bis 2025 voraussichtlich um 40 Prozent auf über 800 EByte wachsen wird, erfüllt PCI-SIG weiterhin die zukünftigen Anforderungen von Speicheranwendungen«, sagt Greg Wong, Gründer und Principal Analyst bei Forward Insights. »Mit dem Übergang der Speicherbranche zu PCIe 4.0 und kurz vor der Einführung der PCIe-5.0-Technologie, werden Unternehmen damit beginnen, PCIe 6.0 in ihre Roadmaps aufzunehmen, um ihre Produkte zukunftssicher zu machen und die Vorteile der hohen Bandbreite und niedrigen Latenz der PCI Express-Technologie zu nutzen.«

Unternehmen wie Cadence und Synopsys bieten bereits seit mehreren Quartalen vorläufige Muster-Implementierungen von PCIe 6.0 an, sodass es wahrscheinlich Unternehmen gibt, die bereits PCIe Gen6-unterstützende Chips entwickeln. Die ersten SSDs, die PCIe 6 unterstützen, dürften aber erst 2024 auf den Markt kommen, wobei Entwickler von Gaming-Systemen üblicherweise die Nase vorn haben.