Vom DRAM über NVDIMM hin zum Persistent-Memory

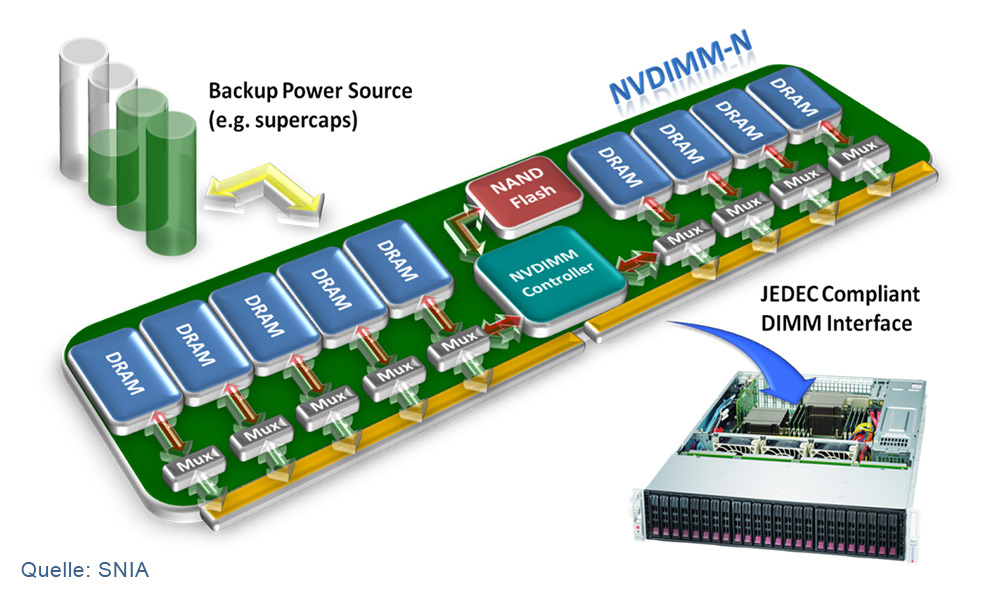

Grafik: SNIADas neue Speichermodul speichert 32 GByte Daten und arbeitet mit Transfergeschwindigkeiten von 6,4 Gbit/s. Bei Kosten von fast 10 Euro pro GByte wird der Hauptspeicherausbau mit vier Modulen und damit 128 GByte schnell 1.000 Euro überschreiten. Doch für Big-Data-Analysen erweisen sich solche für Techniker fantastisch klingende Werte als größere Technologie-Blockade.

Grafik: SNIADas neue Speichermodul speichert 32 GByte Daten und arbeitet mit Transfergeschwindigkeiten von 6,4 Gbit/s. Bei Kosten von fast 10 Euro pro GByte wird der Hauptspeicherausbau mit vier Modulen und damit 128 GByte schnell 1.000 Euro überschreiten. Doch für Big-Data-Analysen erweisen sich solche für Techniker fantastisch klingende Werte als größere Technologie-Blockade.

NVDIMM-N

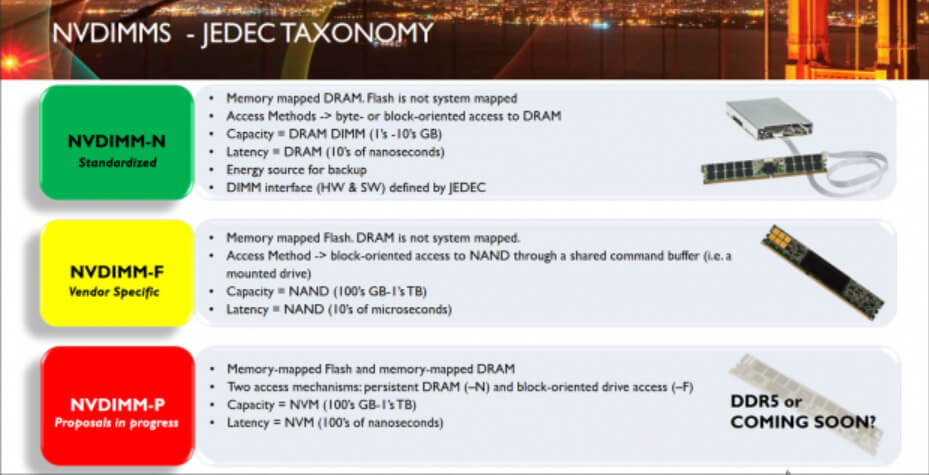

Vergleich der JEDEC-Klassifizierung der drei NVDIMM-Typen (Quelle: Jedec).Der technische Sprung vorwärts ist allerdings in Sichtweite. Ebenfalls in Kürze wird die Jedec den Standard NVDIMM-P verabschieden. Bislang wurden bereits NVDIMM-N und NVDIMM-F ins Leben gerufen und sind auf dem Markt verfügbar. Bei der N-Variante steht hinter jeder DRAM-Speicherzelle eine Flash-Zelle als Backup-Kopie zur Verfügung. Stromausfälle oder Server-Abstürze behindern den Workflow nicht länger. Die F-Variante ist ein miniaturisierter Hybridspeicher auf einem Memory-Modul dar, der wie eine SSD angesprochen wird und hot und warm Data hin- und herschiebt.

Vergleich der JEDEC-Klassifizierung der drei NVDIMM-Typen (Quelle: Jedec).Der technische Sprung vorwärts ist allerdings in Sichtweite. Ebenfalls in Kürze wird die Jedec den Standard NVDIMM-P verabschieden. Bislang wurden bereits NVDIMM-N und NVDIMM-F ins Leben gerufen und sind auf dem Markt verfügbar. Bei der N-Variante steht hinter jeder DRAM-Speicherzelle eine Flash-Zelle als Backup-Kopie zur Verfügung. Stromausfälle oder Server-Abstürze behindern den Workflow nicht länger. Die F-Variante ist ein miniaturisierter Hybridspeicher auf einem Memory-Modul dar, der wie eine SSD angesprochen wird und hot und warm Data hin- und herschiebt.

NVDIMM-F

Die Latenzzeiten auf den nichtflüchtigen Speicher (NV) liegen im gehobenen Mikrosekundenbereich, so dass hier der DRAM-Hauptspeicher als Cache für den schnelleren Zugriff fungiert. Solche herstellerspezifischen Hybridspeichermodule sind schon heute erhältlich und kombinieren in der zweiten Produktgeneration 32 GByte DDR4-DRAM mit einem TByte persistenter Speicherkapazität. Ob hier zukünftig neben NAND-Flash auch Phase Change Memory (PCM), MRAM oder 3D Xpoint eingesetzt werden wird, ist wahrscheinlich eine Platz- und Preisfrage. Das Hybridmodul insgesamt ist nicht als persistenter Speicher ausgelegt, da die Speicherzelleninhalte des DRAM-Caches nicht zurückgeschrieben werden.

NVDIMM-P

Zukunftsträchtig dürfte jedoch der Jedec-Standard NVDIMM-P sein. Hier entsteht eine Speicherarchitektur, die in Miniaturbauform und im Nanosekunden-Zugriffsbereich die Zugriffskette von DRAM, Flash und Festplatte mit ganz viel Cache konsolidiert. Doch statt bei einem »Read-Miss« zig Millisekunden-lang auf ein Datum zu warten, spielt sich die Latenz bei NVDIMM-P im 100 Nanosekunden-Bereich ab.

Die P-Variante braucht allerdings einige Modifikationen im Speicherkanal-Protokoll, da der Zugriff auf große Datenmengen im Terabyte-Bereich mit persistentem Speicher zu organisieren ist. Im Gegensatz zu Flash-Speicher, der üblicherweise über einen I/O-Bus wie PCIe oder USB mit der CPU kommuniziert, wird Persistent Memory von der CPU über den Memory-Bus angesprochen werden. Ein Controller auf dem Speichermodul sorgt dafür, dass die benötigten Daten im Cache stehen oder schnellstmöglich aus dem Persistent Memory dahin gelangen.

Out-of-Order-Execution

Mit solchen Anforderungen ist der deterministische Memory-Bus überfordert. Er unterstützt beispielsweise:

- keine variablen Zugriffszeiten,

- keine gemischten Medienformate,

- kann nicht mit »Read miss« umgehen

- und ist durch Speicheradress-Limitierung auf Kapazitäten von maximal 512 GByte beschränkt.

Intel und AMD müssten insofern die CPU-Memory-Schnittstelle mit zusätzlichen Registern überarbeiten, damit fehlende Dateninhalte im Speichermodul nachgeladen werden können (Out-of-order), der größere Adressbusbereiche ansprechen kann und der auch als Shared-Memory in Cluster-Konfigurationen fungieren kann. So schön flott das alles klingt, es hätte den Nachteil, dass die angedeuteten Änderungen den Betrieb klassischer Software verunmöglichen würden.

Rückschritt Kompatibilität

Die Speicherindustrie wird es also machen wie die PC-Industrie es schon immer gemacht hat, sie wird Rückwärtskompatibilität einbauen, die dann vornehm als NVDIMM-X oder -P+ bezeichnet werden könnte. Dieser Kompatibilitätsmodus wird wie im SSD-Betrieb mit Blockzugriffen und Wear-Levelling Lese- und Schreiboperationen arbeiten. Byte-Zugriffe wie bei DRAMs sind nicht vorgesehen. So müssen Software-Entwickler nur den Gerätetreiber, nicht aber ihre Software anpassen.

Rein theoretisch sind einige Formen von Persistent-Memory so schnell wie DRAMs. Doch man sieht, wie schwer es der Halbleiterindustrie fällt PCM- oder Memristoren zur Produktionsreife zu bringen. Da wird wohl noch ein Jahrzehnt und mehr verstreichen, bis solche Speicher das DRAM kostengünstig ersetzen.

- Schneller auf Daten warten: Die NVMe-Strategie – Teil 1

- SNIA: Persistent Memory and NVDIMM Special Interest Group

- SSD: 2018 bringt den Durchbruch für NVMe

- Technische Grundlagen: Einführung in NVMe

- UNH bietet Interoperabilitäts-Tests für NVMe-oF und NVMe-oE

- So eignet sich Flash über PCIe

- Doc Storage: Was ist NVMe?

- Doc Storage: Was sind NVDIMMs?

- Doc Storage: Was ist Persistent-Memory?