IBM kommt bei »Phase Change Memory«-Forschung kräftig voran

Auch wenn Flash gerade zu einem Siegeszug durch die Datacenter ansetzt, die nächsten Halbleitertechnologien werden in den Laboren dieser Welt schon entwickelt. IBM-Forscher kamen jetzt bei der »Phase Change Memory«-Technologie (PCM) kräftig voran, und demonstrieren drei Bits pro Speicherzelle.

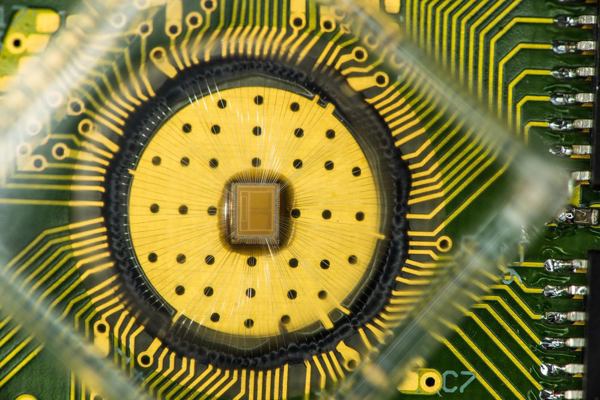

Ein PCM-Chip, der drei Bits pro Speicherzelle speichern kann (Bild: IBM Research)Mit der zuverlässigen Speicherung und Erhaltung von drei Datenbits pro Zelle haben Wissenschaftler von IBM Research in Rüschlikon bei Zürich einen wichtigen Meilenstein in der Entwicklung von Phasenwechselspeichern (Phase Change Memory oder kurz PCM) demonstriert. Die neuesten Forschungsergebnisse verleihen der Entwicklung von noch schnelleren, nichtflüchtigen Speichern auf Basis von PCM neuen Schub. Zum Einsatz könnte diese Art von Speicher insbesondere in Smartphones, bei Komponenten im Internet der Dinge und Industrie 4.0 sowie in hochwertigen Cloud-Speichern für Unternehmen kommen.

Ein PCM-Chip, der drei Bits pro Speicherzelle speichern kann (Bild: IBM Research)Mit der zuverlässigen Speicherung und Erhaltung von drei Datenbits pro Zelle haben Wissenschaftler von IBM Research in Rüschlikon bei Zürich einen wichtigen Meilenstein in der Entwicklung von Phasenwechselspeichern (Phase Change Memory oder kurz PCM) demonstriert. Die neuesten Forschungsergebnisse verleihen der Entwicklung von noch schnelleren, nichtflüchtigen Speichern auf Basis von PCM neuen Schub. Zum Einsatz könnte diese Art von Speicher insbesondere in Smartphones, bei Komponenten im Internet der Dinge und Industrie 4.0 sowie in hochwertigen Cloud-Speichern für Unternehmen kommen.

Die aktuelle Speicherlandschaft reicht von DRAM-Technologie über Festplatten bis hin zu den allgegenwärtigen Flash-Speichern. In den letzten Jahren hat PCM als eine mögliche neue, universelle Speichertechnologie vermehrt Aufmerksamkeit auf sich gezogen, da sie als nichtflüchtiger Speicher eine attraktive Kombination von Lese- und Schreibgeschwindigkeit, Haltbarkeit und Speicherdichte bietet. Eine weitere neuartige Speichertechnologie und möglicher Flash-Nachfolger ist »3D Xpoint«, an der derzeit Intel und Micron Technology stark arbeiten.

Die IBM-Forscher sehen PCM sowohl als eigenständigen Speicher sowie auch in Kombination mit Flash für Anwendungen, in denen die Technologie als extrem schneller Cache-Speicher dient. So könnte beispielsweise das Betriebssystem eines Mobiltelefons in PCM gespeichert werden, um ein sekundenschnelles Starten zu ermöglichen. Unternehmen könnten ihre Datenbanken in PCM speichern, um Abfragen für zeitkritische Online-Anwendungen wie Finanztransaktionen in Rekordzeit durchzuführen.

So funktioniert »Phase Change Memory« (PCM) im Prinzip

Die so genannten Phasenwechselmaterialien weisen zwei stabile Zustände auf: eine amorphe und eine kristalline Phase mit tiefer bzw. hoher elektrischer Leitfähigkeit. Um nun eine »1« oder eine »0« – also ein Bit – in einer PCM-Zelle zu speichern, wird ein hoher oder mittlerer elektrischer Strom an das Material angelegt. Durch entsprechende Programmierung kann die »0« in die amorphe Phase und die »1« in die kristalline Phase geschrieben werden, oder umgekehrt. Das Auslesen des Bits erfolgt dann durch die Detektion des Widerstandes mittels Anlegen eines schwachen Stromflusses. Dieses Verfahren liegt auch den wiederbeschreibbaren Blu-Ray-Optical-Disks zu Grunde.

Forscher von IBM und anderen Institutionen haben bereits erfolgreich dieses Funktionsprinzip für die Speicherung von einem Bit pro Zelle in PCM demonstriert. Anlässlich des IEEE International Memory Workshop zeigen die IBM-Forscher nun erstmals die Speicherung von drei Bits pro Zelle in einer Anordnung aus 64.000 Zellen und einer Ausdauerbelastung von einer Million Zyklen.

»Phase Change Memory« mit Eigenschaften von DRAM und Flash

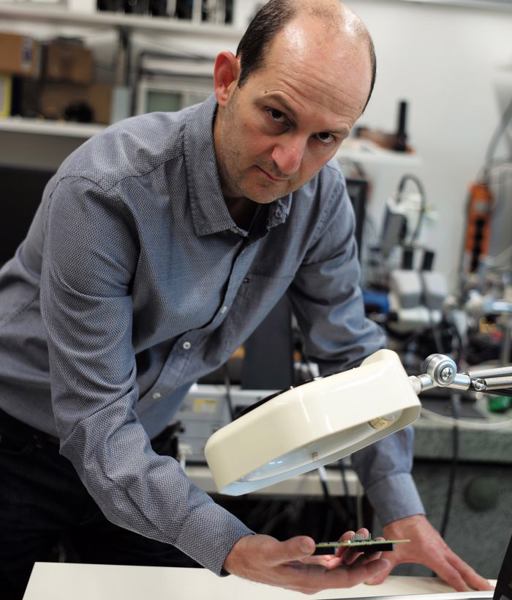

Dr. Haris Pozidis, Non-Volatile Memory Forschungsgruppe, IBM Research – Zürich»Phase Change Memory ist die erste Realisierung eines universellen Speichers mit Eigenschaften sowohl von DRAM als auch Flash. Damit antwortet die Technologie auf eine der zentralen Herausforderungen unserer Industrie«, erklärt Dr. Haris Pozidis, einer der Autoren und Manager der Non-Volatile Memory Forschungsgruppe bei IBM Research – Zürich. »Die Fähigkeit, drei Bits pro Zelle zu speichern, ist ein wichtiger Meilenstein für PCM, denn bei dieser Speicherdichte liegen die Kosten für PCM deutlich unter denen von DRAM und viel näher an denen von Flash.«

Dr. Haris Pozidis, Non-Volatile Memory Forschungsgruppe, IBM Research – Zürich»Phase Change Memory ist die erste Realisierung eines universellen Speichers mit Eigenschaften sowohl von DRAM als auch Flash. Damit antwortet die Technologie auf eine der zentralen Herausforderungen unserer Industrie«, erklärt Dr. Haris Pozidis, einer der Autoren und Manager der Non-Volatile Memory Forschungsgruppe bei IBM Research – Zürich. »Die Fähigkeit, drei Bits pro Zelle zu speichern, ist ein wichtiger Meilenstein für PCM, denn bei dieser Speicherdichte liegen die Kosten für PCM deutlich unter denen von DRAM und viel näher an denen von Flash.«

Um mehrere Bits pro Zelle speichern zu können, haben die IBM-Forscher mehrere neuartige Technologien entwickelt: Verschiedene Verfahren zur Messung des Zellzustandes, die gegen den so genannten Drift (der schleichenden Veränderung der Stabilität der elektrischen Leitfähigkeit der Zelle) immun sind sowie neue drift-tolerante Kodierungs- und Detektionsverfahren.

Gegen den Drift, denn Drift verändert die Stabilität

Die neuen Verfahren zur Messung des Zellzustandes erfassen eine physikalische Eigenschaft der PCM-Zelle, die keiner Veränderung im Laufe der Zeit und somit auch keiner Veränderung durch Drift unterliegt. Für zusätzliche Robustheit der in einer Zelle gespeicherten Daten gegenüber Temperaturschwankungen der Umgebung sorgt zudem ein neuartiges Kodierungs- und Detektionsverfahren. Dieses Verfahren passt die Schwellwerte, die verwendet werden, um die in der Zelle gespeicherten Informationen zu detektieren, auf adaptive Weise an, so dass sie den Veränderungen aufgrund von Temperaturschwankungen folgen. Somit kann der Zellzustand zuverlässig auch nach Ablauf einer beträchtlichen Zeit nach der Programmierung des Speichers ausgelesen werden. Der Speicher ist damit also nichtflüchtig.

»Dank dieser Fortschritte lassen sich die großen Herausforderungen der Mehrbit-PCM-Speicherung wie Drift, Variabilität, Empfindlichkeit auf Temperaturschwankungen und Belastbarkeit durch Schreibzyklen erfolgreich meistern«, erklärt Dr. Evangelos Eleftheriou, IBM Fellow und Leiter der Abteilung Cloud & Computing Infrastructure.

Die IBM-Forscher verwendeten einen experimentellen Multi-Bit-PCM-Chip, der mit einer integrierten Standard-Leiterplatte verbunden war. Der Chip besteht aus einer Anordnung von 2x2 Millionen Zellen, die in vier Bereiche unterteilt sind und auf die nacheinander durch die Systemarchitektur (interleaving architecture) zugegriffen wird. Die Speichereinheit ist laut IBM 2×1000 μm x 800 μm gross. Die PCM-Zellen basieren auf einer dotierten Chalkogenid-Legierung, und wurden auf einem Prototyp-Chip in 90-nm-CMOS-Baseline-Technologie integriert, der als Charakterisierungsplattform dient.

Power8-Server mit PCM-Speicher demonstriert

IBM Wissenschaftler demonstrierten am »OpenPOWER Summit« im US-amerikanischen San Jose im April dieses Jahres erstmals die Kombination von Phase Change Memory mit Power8-Servern (gebaut von IBM und Tyan Computer) mittels eines CAPI-Protokolls (Coherent Accelerator Processor Interface). Diese Technologie profitiert von der kurzen Latenzzeit und hohe Zugriffsgranularität (engl. access granularity) von PCM sowie von der Effizienz der Open-Power-Architektur und des CAPI-Protokolls.

In der gezeigten Demonstration haben die Wissenschaftler sehr geringe und konsistente Wartezeiten für 128-Byte Lese- und Schreibvorgängen zwischen den PCM-Chips und dem Power8-Prozessor gemessen.

IBM-Forscher Dr. Haris Pozidis erläutert die PCM-Technologie

- IBM Research – Zürich

- Flash-Lösungen von IBM

- IBM: Cognitive Storage agiert wie menschliches Gehirn

- IBM-Ausblick auf kommende Halbleitertechnologien

- IBM-Roadshow #WhatsUpIBM informiert über intelligente Infrastrukturen

- Interview mit Samsung-Manager Thomas Arenz: Datacenter haben hohes Einsparpotenzial durch 3D bei DRAM und Flash

- IBM pocht auf Storage-Dreieinigkeit: Appliance, Software und Cloud